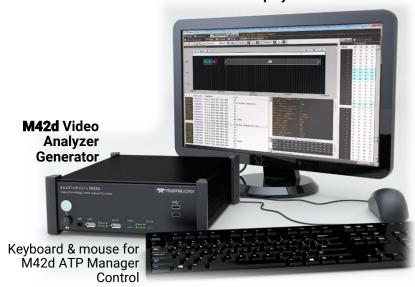

# quantumdata™ M42d DisplayPort 2.0 Video Analyzer/Generator

# Full 80Gb/s Link Rate Functional and Compliance Tester

### **Key Features**

- Equipped with both DP standard and USB-C ports for Tx and Rx functions

- Test DP sources 10Gb/s,13.5Gb/s & 20Gb/s lane rates at the new 128b/132b line coding

- View incoming video and metadata—including DSC compressed--from a source device

- Capture and decode incoming video, protocol, control packets including Display Stream Compression (DSC)

- Video generator to test displays and monitors at UHBR lane rates with large format & image library

- Configure link training parameters to test display's handling of link training on video generator

- Generate Display Stream Compression (DSC), select patterns and configure slices and video parameters

- View and edit EDID and DPCD registers

- Monitor Aux Channel transactions while emulating a DP 1.4 or DP 2.0 source or sink

- Passively monitor the Main Link and Aux Channel between a source & display at all UHBR lane rates

- Run tests on source and NEW! sink devices with Panel Replay capability

- Support for LTTPR in non-transparent mode for 128b/132b at UHBR rates at 8b/10b line code for lane rates up to HBR3

- View Power Delivery (PD) protocol negotiations for USB-C DP Alt Mode

- UPDATED! DP 2.0 Link Layer compliance tests on source & sink devices up to 20.0Gb/s per lane

- NEW TESTS! DP 2.0 LTTPR compliance tests on source & sink devices up to 20.0Gb/s per lane

- UPDATED! DP Adaptive Sync compliance tests on source and sync devices

- NEW! Run DP Adaptive Sync functional tests on source and sync devices

- Run approved DP 1.4 Link Layer compliance tests on sources and sinks up to 8.1Gb/s per lane

- Run DP 1.4 Forward Error Correction (FEC) and Display Stream Compression (DSC) compliance tests for sources and sinks

- Run HDCP 2.2/3 compliance tests on DisplayPort sources, sinks and branch devices

- Run audio tests using LPCM sine wave audio tones

- Run Golden Frame PRN error tests on sources and in loopback configuration

- Run tests on embedded DisplayPort (eDP) 1.4b sources and panels (limited)

- UPDATED! Application Programming Interface (API) for automated testing for compliance & functional testing.

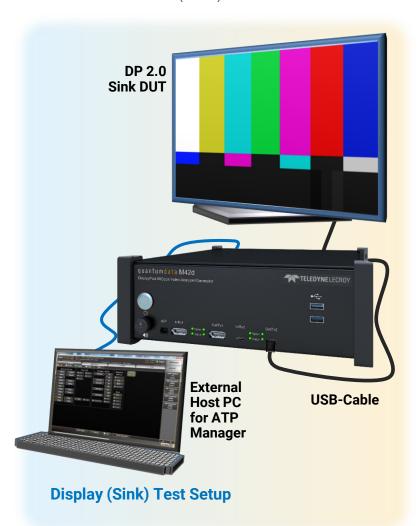

The Teledyne LeCroy quantumdata M42d Video Analyzer/Generator provides an unprecedented combination of functional and compliance testing for video, audio and protocol of DisplayPort 2.0 and DisplayPort 1.4. The M42d supports legacy DisplayPort lane rates of 1.62, 2.7, 5.4, 8.1 Gb/s and the new DP 2.0 higher speed lane rates and new line coding—128b/132b—of 10.0, 13.5 & 20.0Gb/s data rates up to 4 lanes. The protocol analyzer provides a snapshot status view and deep analysis using captures of incoming DisplayPort 2.0 (and DP 1.4) streams from source devices including DSC/FEC compressed streams. The M42d's video generator can be used for testing silicon development boards, displays, docking stations and hubs, USB-C adapters, extenders, etc. The video generator offers a large library of standard video timings and test patterns necessary for testing next generation high resolution displays.

The M42d supports a full suite of DP 1.4 link layer, forward error correction (FEC) and display stream compression (DSC) compliance tests for both sources and sinks. (Compliance tests for DP 2.0 are currently being implemented.)

The Passive Probe feature based on Teledyne LeCroy's cutting-edge T.A.P.4™ technology, enables full monitoring of the DisplayPort Main Link and the Aux Channel between two DisplayPort devices up to 20 Gb/s lane rates future.

### **Operation**

The M42d supports generation and analysis of the DisplayPort data streams through the user-friendly ATP Manager. The M42d can be controlled through the ATP Manager operated either via a laptop connected to the M42d RJ45 LAN port or through a USB keyboard and mouse and a connected UHD HDMI admin display.

# **DISPLAY TESTS - VIDEO TESTING**

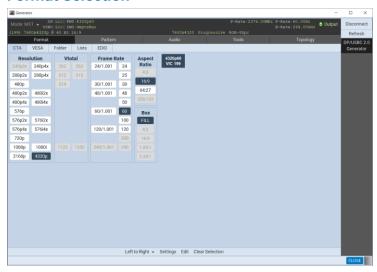

### **Video Generation**

The M42d supports video and audio functional testing at UHBR lane rates up on 1, 2 and 4 lanes to support high resolution formats. The M42d has an extensive set of video formats and library of test patterns. You can specify lane configurations for link training (below).

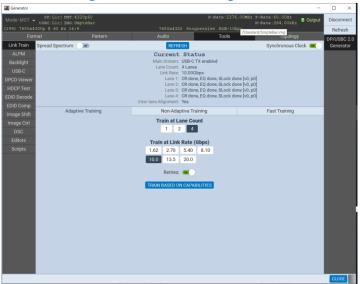

### **Link Training Control and Configuration**

### **Format Selection**

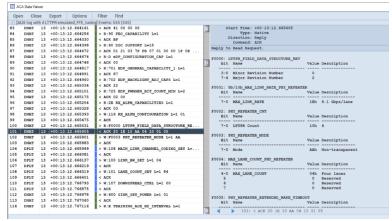

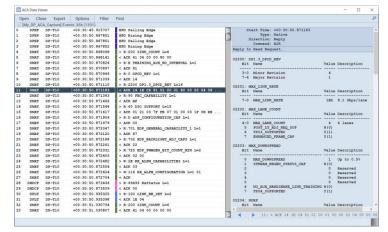

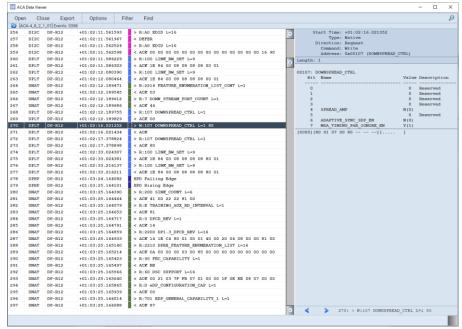

### **Aux Channel Analyzer (ACA)**

The M42d 's Auxiliary Channel Analyzer (ACA) feature enables you to monitor the DP Aux Channel for link training, MST negotiations, HDCP transactions, DP Alt Mode PD negotiations and EDID exchanges between the M42d Rx port and a connected source. The ACA logs these events and assigns precise timestamps to them. You can view the details of each transaction. These ACA logs can be saved and disseminated for further analysis by colleagues and other subject matter experts.

### **Aux Channel Analyzer**

## **Link Training Control and Configuration**

The M41d 's link training control feature enables you to configure the link training parameters. You can set limits on the lane count and link rate and allow the link training engine to establish link training based on those limitations or you can force link training parameters—lane count, link rate, voltage swing, pre-emphasis.

# **SOURCE TESTS - VIDEO & PROTOCOL ANALYSIS**

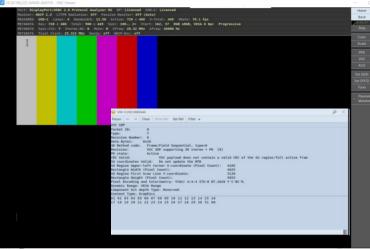

### **Receiver - Basic & Capture Analyzer**

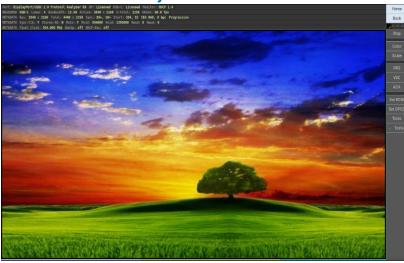

The M42d 's Basic Analyzer enables you to view the incoming video, lanes and link rate, timing, colorimetry and various other metadata in real time at a glance. The Basic Analyzer mode provides a basic confidence test to verify that the incoming video is essentially correct. The Rx port emulates any EDID on to test a source devices handling of various EDIDs. You can also configure DPCD registers for emulating on the DP Rx port using the DPCD Editor.

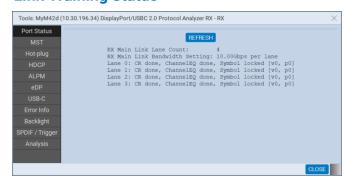

### **Link Training Status**

### **Receiver - Basic Analysis**

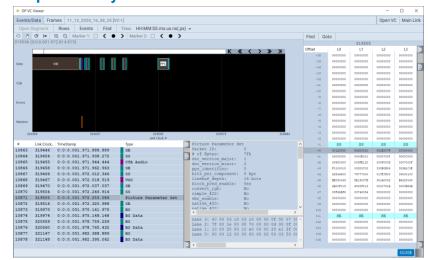

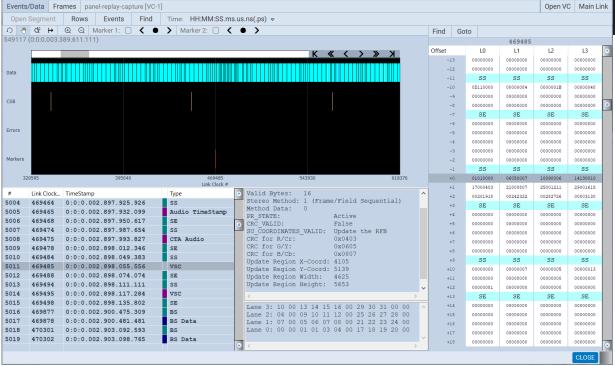

### **Receiver - Capture Analyzer**

The deep Capture Analyzer enables you to view the protocol data of the high-speed link (shown below) and the underlying virtual channels (shown below). The Capture Analyzer provide deep insight into the data, control symbols, video, metadata and protocol data.

### **Capture Analysis (Main Link)**

### **Capture Analysis - Virtual Channels**

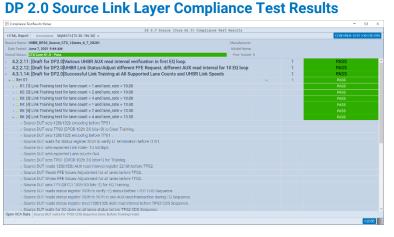

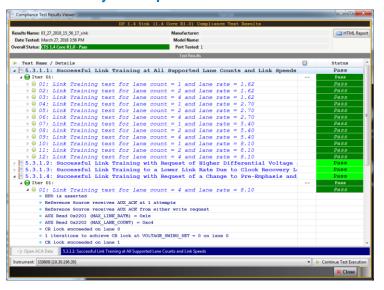

# **DP 2.0/1.4 LINK LAYER SOURCE COMPLIANCE**

### **Source Link Layer Compliance**

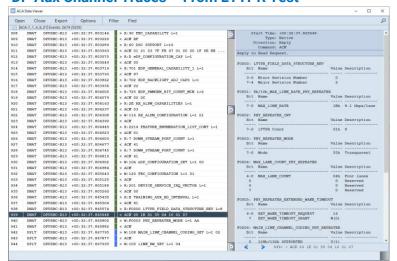

The DP source link layer compliance are ideal for self-testing or pre-testing your HBR3 or UHBR-capable DisplayPort source product prior to submission to an Authorized Test Center for approval. Pre-testing provides added assurance that your product will pass at the ATC when submitted. The compliance tests enable you to view the captured data and detailed test results which help pinpoint the cause of compliance test failures. You can link to the aux channel traces in the Aux Channel Analyzer (ACA) to view the root cause of failures.

### DP 1.4/2.0 Source Link Layer Compliance - Test Selection

### **DP 1.4 Source Link Layer Compliance Test Results**

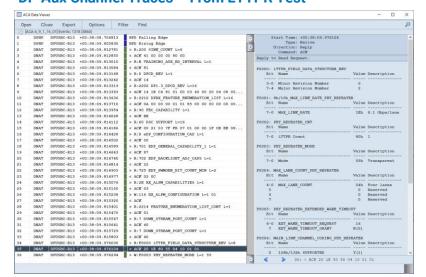

### **DP Aux Channel Traces - From LLC Test**

| Oper |      |    | Export  |                        | Filter Find                                                 |        |                                              |              |             |

|------|------|----|---------|------------------------|-------------------------------------------------------------|--------|----------------------------------------------|--------------|-------------|

| AU   |      |    |         |                        | ng) Events: 535 (535)                                       |        |                                              |              |             |

| 133  | DPLT | 13 | +00:13: | 12.885924              | < ACK 77 77 05 03                                           | 00202  | LANEO 1 STATUS:                              |              |             |

| 134  | DPLT | 13 | +00:13: | 12.887189              | > R:202 LANEO_1_STATUS: L=4                                 |        | t Name                                       | Value        | Description |

| 135  | DPLT | 13 | +00:13: | 12.887263              | < ACK 77 77 05 03                                           |        |                                              |              |             |

| 36   | DPLT | 13 | +00:13: | 12.888479              | > R:202 LANEO_1_STATUS: L=4                                 |        | LANEO_CR_DONE                                | Y(1)         |             |

| 37   | DPLT | 13 | +00:13: | 12.888553              | < ACK 77 77 05 03                                           | 1      | LANEO_CHANNEL_EQ_DONE<br>LANEO SYMBOL LOCKED | Y(1)<br>Y(1) |             |

| 138  | DPLT | 13 | +00:13: | 12.889842              | > R:202 LANEO_1_STATUS: L=4                                 |        | LANEO_SIMBOL_LOCKED                          |              | Reserved    |

| 139  | DPLT | 13 | +00:13: | 12.889916              | < ACK 77 77 05 03                                           |        | LANE1 CR DONE                                | Y(1)         | Neserven    |

| 40   | DPLT | 13 | +00:13: | 12.891175              | > R:202 LANEO 1 STATUS: L=4                                 |        | LANEI CHANNEL EQ DONE                        | Y(1)         |             |

| 41   | DPLT | 13 | +00:13: | 12.891249              | < ACK 77 77 05 03                                           |        | LANE1_SYMBOL_LOCKED                          | Y(1)         |             |

| 42   | DPLT | 13 | +00:13: | 12.892497              | > R:202 LANEO 1 STATUS: L=4                                 |        |                                              | 0            | Reserved    |

| 43   | DPLT | 13 | +00:13: | 12.892571              | < ACK 77 77 05 03                                           | 00000  | LANE2 3 STATUS                               |              |             |

| 44   | DPLT | 13 | +00:13: | 12.893836              | > R:202 LANEO 1 STATUS: L=4                                 |        | t Name                                       | Walne        | Description |

| 45   | DPLT | 13 | +00:13: | 12.893910              | < ACK 77 77 0D 03                                           |        |                                              |              |             |

| 46   | DPLT | 13 | +00:13: | 12.894090              | > W:102 TRAINING PATTERN SET: L=1 00                        |        | LANE2 CR DONE                                | Y(1)         |             |

| 47   | DPLT | 13 | +00:13: | 12.894172              | < ACK                                                       | 1      | LANE2_CHANNEL_EQ_DONE                        | Y(1)         |             |

| 48   | DNAT |    |         | 12.894360              | > R:200 SINK COUNT L=6                                      |        | LANE2_SYMBOL_LOCKED                          | Y(1)         | _           |

| 49   | DNAT |    |         | 12.894434              | < ACK 41 00 77 77 0D 02                                     | 2      | LANES CR DONE                                | Y(1)         | Reserved    |

| 150  | DPLT |    |         | 12.894688              | > R:100 LINK BW SET L=9                                     |        | LANES CHANNEL EQ DONE                        | Y(1)         |             |

| 51   | DPLT |    |         | 12.894762              | < ACK 04 84 00 05 05 05 05 00 02                            |        | LANES SYMBOL LOCKED                          | Y(1)         |             |

| 52   | DNAT |    |         | 12.894898              | > R:200 SINK COUNT L=8                                      | -      |                                              | 0            | Reserved    |

| 53   | DNAT |    |         | 12.894972              | < ACK 41 00 77 77 0D 02 66 66                               |        |                                              |              |             |

| 54   | DPLT |    |         | 12.896928              | > R:100 LINK BW SET L=9                                     |        | LANE_ALIGN_STATUS_UPDATED                    |              | Description |

| 55   | DPLT |    |         | 12.897002              | < ACK 04 84 00 05 05 05 05 00 02                            |        | t Name                                       | AWTHE        | pescription |

| 56   | DPLT |    |         | 12.900671              | > R:100 LINK BW SET L=9                                     |        | INTERLANE ALIGN DONE                         | Y(1)         |             |

| 57   | DPLT |    |         | 12.900745              | < ACK 04 84 00 05 05 05 05 00 02                            | 1      | POST LT ADJ REQ IN PROGRESS                  | N(0)         |             |

| 158  | DNAT |    |         | 12.974553              | > R:200 SINK COUNT L=8                                      | - 2    | 128b/132b_DPRX_EQ_INTERLANE                  |              |             |

| 59   | DNAT |    |         | 12.974555              | < ACK 41 00 77 77 0D 03 66 66                               | 3      | 128b/132b_DFRX_CDS_INTERLAN                  |              | ONE Y(1)    |

| 160  | DNAT |    |         | 13.069295              | > R:200 SINK COUNT L=8                                      |        | 128b/132b_LT_FAILED                          | N(0)         | Reserved    |

| 61   |      |    |         |                        | < ACK 41 00 77 77 0D 03 66 66                               |        | DOWNSTREAM PORT STATUS CHAN                  |              | weserved    |

| 62   | DNAT |    |         | 13.069369              |                                                             |        | LINK STATUS UPDATED                          | N(0)         |             |

|      |      |    |         | 13.149956              | > R:100 LINK_BW_SET L=9                                     |        |                                              | 1000000      |             |

| 163  | DPLT |    |         | 13.150030<br>13.150164 | < ACK 04 84 00 05 05 05 05 00 02<br>> R:100 LINK BW SET L=9 | 00205: | SINK STATUS                                  | Walne        |             |

# **DP 2.0/1.4 LINK LAYER SINK COMPLIANCE**

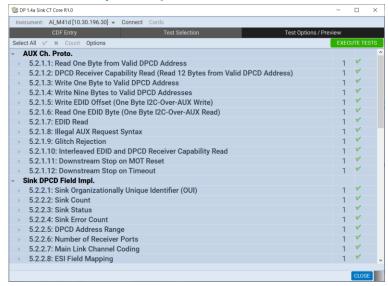

### **Sink Link Layer & EDID Compliance**

The DP sink (display) and EDID/DisplayID and Link Layer compliance tests are ideal for pre-testing or self-testing (where permitted) your DisplayPort display product prior to submission to an Authorized Test Center for approval. Pretesting provides added assurance that your product will pass at the ATC when submitted. The compliance tests (below right) enable you to view the captured data and detailed test results which help pinpoint the cause of compliance test failures. The link layer compliance test suite now includes tests for forward error correction (FEC). You can link to the aux channel traces in the Aux Channel Analyzer (ACA) to view the root cause of failures (below).

### **DP 1.4 Link Layer Compliance - Test Selection**

### **DP 1.4 Link Layer Compliance - Test Results**

### **DP Aux Channel Traces - From LLC Test**

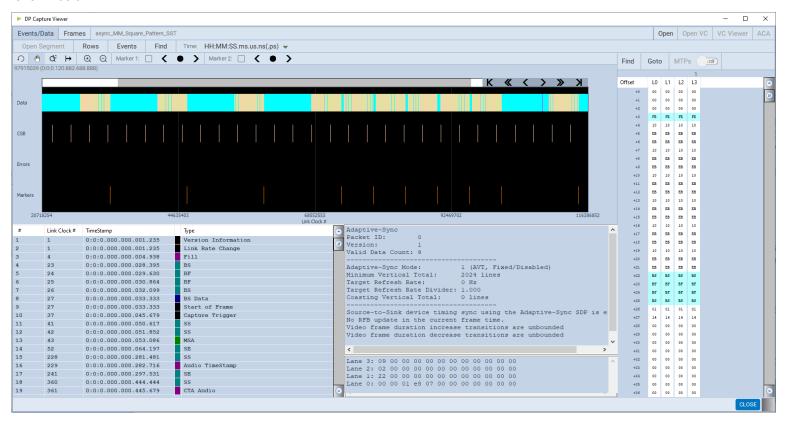

# **ADAPTIVE SYNC FUNCTIONAL TESTING**

### **Adaptive Sync Source Functional Testing**

The M42d now supports the testing of Adaptive Sync-capable source and sink devices for HBR3 rates. The Adaptive Sync analyzer for testing Adaptive Sync-capable source devices enables you to view the variations in the vertical blanking to lower the refresh rate. The Adaptive Sync video generation for testing Adaptive Sync-capable displays or monitors enables you to send different test patterns that increase and decrease the vertical blanking to increase or decrease the refresh rate of the display. Adaptive Sync testing for sink devices is currently only supported through the command line with GUI support to be provided in the future.

### **Adaptive Sync Capture Analysis**

You can view the Adaptive Sync variations in the vertical blanking in the Capture Analyzer as shown below.

### **Adapative Sync Aux Channel Analyzer (ACA)**

You can view the Adaptive Sync discover and configuration transactions occurring over the Aux Channel with the Aux Channel Analyzer (ACA) as shown left.

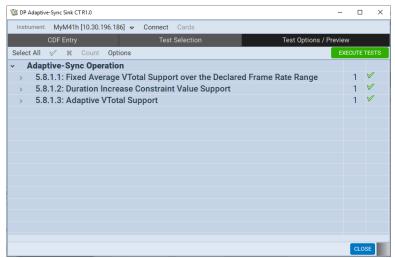

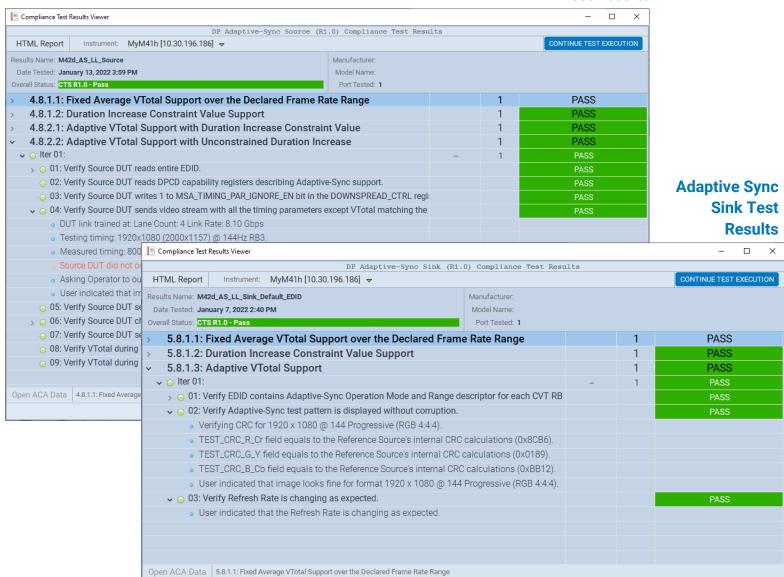

# **ADAPTIVE SYNC COMPLIANCE TESTS**

### **Adaptive Sync Source Compliance Test Selection**

# DP Adaptive Sync Source CTR1.0 Instrument: MyM41h [10.30.196.186] CDF Entry Test Selection Test Options / Preview Select All \*\* Count Options Fixed Average VTotal 4.8.1.1: Fixed Average VTotal Support over the Declared Frame Rate Range 1 \*\* Adaptive VTotal Adaptive VTotal 4.8.2.1: Adaptive VTotal Support with Duration Increase Constraint Value 1 4.8.2.2: Adaptive VTotal Support with Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrained Duration Increase 1 \*\* Adaptive VTotal Support With Unconstrain

### **Adaptive Sync Sink Compliance Test Selection**

### **Adaptive Sync Compliance Testing**

The M42d supports Adaptive Sync compliance testing for both source and sink devices. The examples below (source left, sink right) show the details provided with the compliance test results. Currently tests are provided for rates up to HBR3 with UHBR support coming in a future release.

# Adaptive Sync Source Compliance Test Results

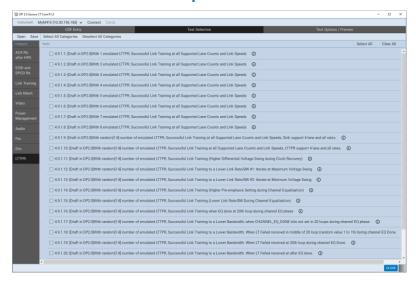

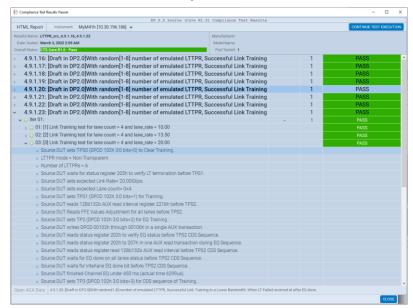

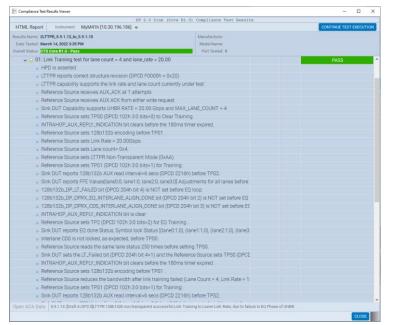

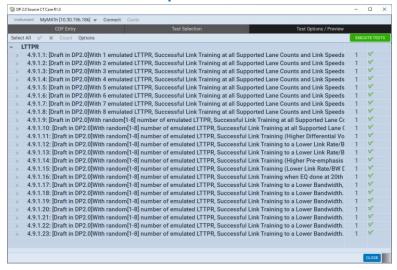

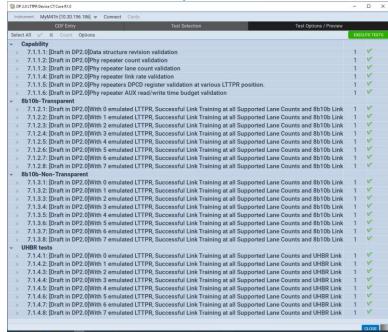

# **DP 2.0 LTTPR SOURCE COMPLIANCE**

### **LTTPR-Capable Source Compliance**

The DP Source Link Training Tunable Phy Repeater (LTTPR) compliance are ideal for self-testing or pre-testing your HBR3 or UHBR-capable DisplayPort source product prior to submission to an Authorized Test Center for approval. Pre-testing provides added assurance that your product will pass at the ATC when submitted. The compliance tests enable you to view the captured data and detailed test results which help pinpoint the cause of compliance test failures. You can link to the aux channel traces in the Aux Channel Analyzer (ACA) to view the root cause of failures.

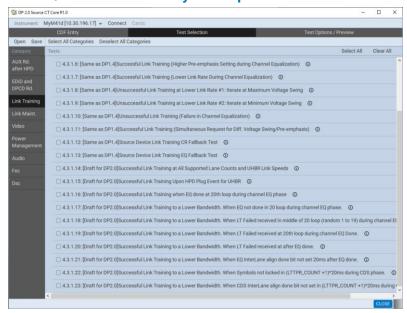

### **DP 2.0 Source LTTPR Compliance - Test Selection**

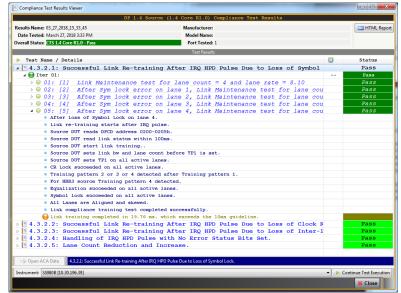

### **DP 2.0 Source LTTPR Compliance Test Results**

### **DP Aux Channel Traces - From LTTPR Test**

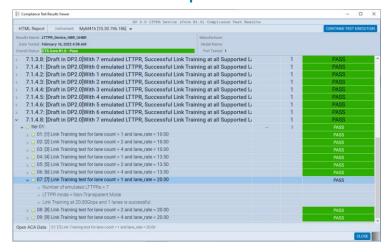

# **DP 2.0 LTTPR SINK/DEVICE COMPLIANCE**

### **LTTPR-Capable Sink & LTTPR Device Compliance**

The DP Sink and Device Link Training Tunable Phy Repeater (LTTPR) compliance are ideal for self-testing or pre-testing your HBR3 or UHBR-capable DisplayPort source product prior to submission to an Authorized Test Center for approval. Pretesting provides added assurance that your product will pass at the ATC when submitted. The compliance tests enable you to view the captured data and detailed test results which help pinpoint the cause of compliance test failures. You can link to the aux channel traces in the Aux Channel Analyzer (ACA) to view the root cause of failures.

### **DP 2.0 LTTPR Device Compliance - Test Selection**

### **DP 2.0 LTTPR Device Compliance - Test Results**

### **DP 2.0 LTTPR Sink Compliance - Test Selection**

### **DP 2.0 LTTPR Device Compliance - Test Results**

### **DP Aux Channel Traces – From LTTPR Test**

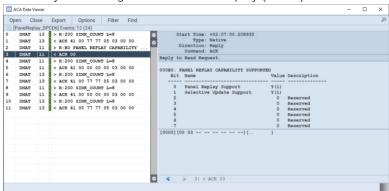

# PANEL REPLAY FUNCTIONAL TESTING

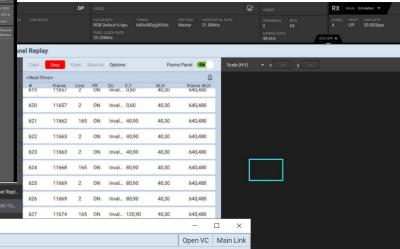

### **Panel Replay Testing**

The M42d's supports functional testing of Panel Replaycapable source and display devices. The analysis support for testing sources provides emulation of a Panel Replay sink device. The Panel Replay sink functional test enables you to configure selected update regions through the command line (GUI implementation is future).

### **Panel Replay Source Analysis**

The Real Time analyzer provides a real time update view (below) showing the incoming Panel Replay VSCs where you can see the changes from the previous frame. The transaction list (below right) shows the Panel Replay VSC metadata packets that have been sent with Selected Update regions. The panel on the right depicts the areas (blue box) where the selected transaction (left panel) VSCs and the SUs have indicated at change.

### **Panel Replay Aux Channel Monitor**

The M42d enables you to view the Aux transactions for discovery and configuration of Panel Replay (below).

### **Capture Analysis**

You can capture the Panel Replay VSC metadata packets in the Capture Analyzer (bottom) where you can examine the VSCs showing the Selected Update (SU) regions per captured frame.

### **Receiver - Analyzer Transaction List**

## Capture Analysis Showing VSCs

DP VC Viewer

### DisplayPort 2.0 Capabilities

| Version                       | Displa  | yPort 2.0 (and DP 1.4)                                               |

|-------------------------------|---------|----------------------------------------------------------------------|

| Standard Video Formats        | VESA,   | CTA CTA                                                              |

| Protocols and Line Coding     | DP, DS  | SC, FEC, MST, SSC, SDP with 128b/132b encoding (LTTPR, Panel Replay) |

| Video Data Rates              | 1.62, 2 | 2.7, 5.4, 8.1, 10.0, 13.5 & 20 Gb/s; 1, 2, 4 Lanes                   |

| Video Encoding / Color Depths | RGB, Y  | /CbCr - 8, 10, 12, 16 bits (6 bits future)                           |

| Video Sampling Modes          | 4:4:4,  | 4:2:2, 4:2:0                                                         |

| HDCP                          | Versio  | ns 1.3 and 2.3                                                       |

| Audio                         | 8 Char  | nnel LPCM programmable sine wave                                     |

| Capture memory                | 8 GBy   | tes                                                                  |

### **Connectors - Front**

| DP Standard | Tx (1) DP Full-Sized; Rx (1) DP Full-Sized                                         |

|-------------|------------------------------------------------------------------------------------|

| USB-C       | Tx (1) USB-C with DP Alt Mode; Rx (1) USB-C with DP Alt Mode                       |

| eDP Header  | Pins to access eDP Tx backlight controls                                           |

| USB (2)     | For connecting keyboard and mouse for ATP Manager control & external storage media |

### Connectors - Back

| HDMI - Admin Connector | HDMI 2.0 Port for external monitor for ATP Manager GUI                                                              |

|------------------------|---------------------------------------------------------------------------------------------------------------------|

| USB (2); USB-C (2)     | Keyboard / mouse connected to USB ports to control ATP Manager on external display connected to Admin HDMI 2.0 port |

| RJ45 E1                | For admin control over LAN from computer running ATP Manager                                                        |

| Cross Sync connector   | Use for triggering a capture or for a capture event to trigger an oscilloscope (future)                             |

| All other connectors   | Not used                                                                                                            |

### Physical/Electric/Admin

| Power                | 100-240 VAC, 50-60 Hz, 200 Watts                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------|

| Size / Weight        | Height: 3.44 in. (8.74 cm) Width: 9.57 in. (24.30 cm) Depth: 10.94 in. (27.79 cm) - 7.6 LBS; 5.057 Kg |

| Rack mountable       | 2 RU mounts in 19-inch rack with rack mounting brackets                                               |

| Internal speaker     | Speaker with volume control for monitoring incoming LPCM audio (future)                               |

| Command Line Control | Ethernet (RJ-45) for external GUI                                                                     |

| System Control       | External PC connected over LAN to Ethernet RJ45, VNC or Keyboard/mouse and 4K TV at Admin HDMI port   |

| Environmental        | Operating Temp: 32 to 104 (F); 0 to 40 (C)                                                            |

### Ordering/Product Code Description

| 00-00259      | M42d UHBR Video Analyzer/Generator (This is the Hardware System with basic video generation and analysis)       |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| 00-00261      | M42d HBR3 Video Analyzer/Generator (This is the Hardware System with basic video generation and analysis)       |

| 95-00221      | M42d Upgrade from HBR3 00-00261 System to UHBR rates with 00-00259 System                                       |

| 95-00222      | Passive Probing Main Link and Aux Channel                                                                       |

| 95-00225      | Sink Enhanced Functional test - Includes DSC, LTTPR, Panel Replay & Adaptive Sync Functional Tests              |

| 95-00226      | Source Enhanced Functional test - Includes DSC, Capture Analysis, LTTPR, Panel Replay, Adaptive Sync Functional |

| 95-00227      | DP 1.4 Sink EDID/DisplayID compliance tests (requires 95-00225)                                                 |

| 95-00228      | DP 1.4 Source EDID/DisplayID compliance tests (requires 95-00226)                                               |

| 95-00232      | DP 1.4/2.0 Source Link Layer & (MST future) compliance tests                                                    |

| 95-00232      | (DP 2.0 tests not fully supported; full suite future) (requires 95-00226)                                       |

| 95-00233      | DP 1.4/2.0 Sink Link Layer & (MST future) compliance tests                                                      |

| 95-00255      | (Limited DP 2.0 tests currently supported; full suite future) (requires 95-00225)                               |

| 95-00236      | DP 1.4/2.0 DSC/FEC Source compliance tests (DP 2.0 tests are future) (requires 95-00226)                        |

| 95-00237      | DP 1.4/2.0 DSC/FEC Sink compliance tests (DP 2.0 tests are future) (requires 95-00225)                          |

| 95-00240 NEW! | DP 1.4/2.0 LTTPR Source compliance tests (requires 95-00226)                                                    |

| 95-00241 NEW! | DP 1.4/2.0 LTTPR Sink compliance tests (requires 95-00225)                                                      |

| 95-00242 NEW! | DP 1.4/2.0 LTTPR Device compliance tests (requires 95-00225 & 95-00226)                                         |

| 95-00234      | DP 1.4/2.0 Adaptive Sync Source compliance test (support for DP 2.0 UHBR rates is future) (requires 95-00226)   |

| 95-00235      | DP 1.4/2.0 Adaptive Sync Sink compliance test (support for DP 2.0 UHBR rates is future) (requires 95-00225)     |

| 95-00214      | HDCP 2.3 Source compliance tests (requires 95-00226)                                                            |

| 95-00217      | HDCP 2.3 Sink compliance tests (requires 95-00225)                                                              |

| 95-00212      | Embedded DisplayPort (eDP) (Limited functions supported)                                                        |

| 95-00209      | M41x Rack-mount Kit                                                                                             |

### 绿测科技有限公司

广州总部:广州市番禺区陈边村金欧大道83号江潮创意园A栋208室

深圳分公司:深圳市龙华区龙华街道油松社区东环一路1号耀丰通工业园1-2栋2栋607南宁分公司:广西自由贸易试验区南宁片区五象大道401号五象航洋城1号楼3519号

广州分公司:广州市南沙区凤凰大道89号中国铁建·凤凰广场B栋1201房

电话: 020-2204 2442 传真: 020-8067 2851

邮箱: Sales@greentest.com.cn 官网: www.greentest.com.cn

微信视频号

绿测科技订阅号

绿测工场服务号